1 半導体入門

1.1 半導体とは?

価電子帯と伝導帯の間の 禁制帯 (band gap) が十分に小さくて遷移を制御することが可能で,基底状態では価電子帯は完全に埋まっているものの伝導帯は空いているような物質を 半導体 という.1

このような半導体では,熱や光,また外部電磁場などにより価電子が励起され,伝導帯に移る.この電子に加えて,価電子帯に生じた正孔も導電性に寄与する.2 この 正孔 (hole) を擬似的に粒子と扱い,正孔の波動方程式を議論したのが (Heisenberg, 1931) である.

1.2 半導体発見の歴史

(Faraday, 1833) は,通常金属では温度の上昇と共に電気抵抗が増すが,硫化銀 Ag2S を初めとしたいくつかの物質では逆に電気抵抗が減少することを報告している.

(Braun, 1874) は 方鉛鉱 PbS に電流を流そうとしても,単一方向にしか電流が流れない整流作用を示すことを発見し,3 その後20世紀に入るとラジオに応用された.これが人類が初めて出会った半導体デバイスだったと言える (Sze and Lee, 2012, p. 1).4

Braun はその後ブラウン管を発明し,こちらの業績により 1909 年にノーベル物理学賞を受賞する.

(Round, 1907) はダイオードが電界を印加することで発行することがある (electroluminescence) ことを発見した.

1.3 基本用語のまとめ

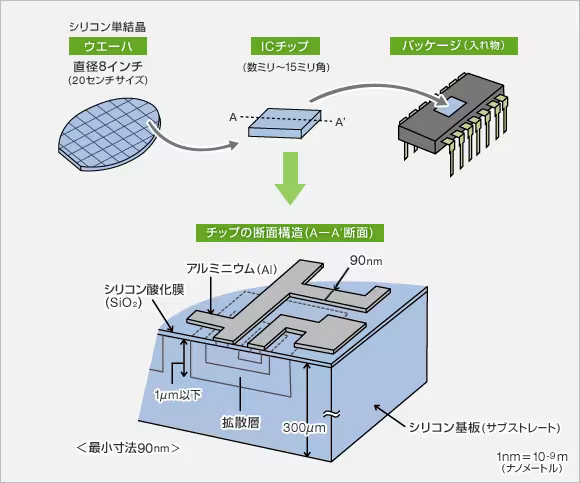

半導体素子には,トランジスタやダイオードなどがある.これらを配線によって相互接続したものが IC チップである.IC チップはシリコンのインゴットを円板状に切り出した ウエハ (wafer) 上に構築する.IC チップは平面的な印象を受けるが,実際は層に分けて構成されている,高度に立体的な構造物である.

一つのウエハから多数のチップが作成され,その各単位を ダイ (die) ともいう.

しかし,普段我々が目にする IC チップ は パッケージ されたもの,で.IC チップそのもの(ダイそのもの)を目にすることはない.

32nm などというときは,ダイの大きさではなく,ダイ上の最小のトランジスタのサイズをいう.5

1.4 集積回路が出来るまで

まず回路を設計し,原版(マスター)を作る.これを フォトマスク (photomask) または レティクル (reticle) という.

これをウエハに転写するには,フォトリソグラフィ (Photolithography) を用いる.シリコンウエハの形成は,Czochralski 法 (Czochralski, 1918) による.6

リソグラフィ自体は 1798 年からあり,Niépce が 歴青 が感光剤の役割を果たすことを発見し,カメラの発明と同時に発見された.

エッチングに耐性のある感光剤を使えば,半導体デバイスの製造に応用できると気づいたのは (Andrus, 1957) である.この技術は半導体製造コストの 35 %を占めており,半導体市場の急成長はほとんどこの技術の進歩と両輪であると言う者も多い.7

シリコン表面に酸化被膜を形成することで不純物原子の移動を阻止できることは (Frosch and Derick, 1957) が発見した.

以上の技術を用いて,最初の IC は (Kilby, 1959) が作った.Jack Kilby はその後 2000 年にノーベル物理学賞を受賞する.

しかし真に大量生産可能にし,半導体産業を大きくしたのは (Noyce, 1959) の発明であった.これは,現在主流の製法の基である Planar Process (Hoerni, 1960) で作られた.

実際に,どのように半導体チップを製造するかについては次節 2 で詳しく解説する.

2 半導体の製造

半導体の製造段階は,典型的には次の3つに大別される.

- 設計

- 回路・レイアウト作成 (design)

- フォトマスク (photomask) 作成

- 前工程:次の3工程を繰り返ことで何層もの膜を積層する

- 成膜 (deposition)

- パターン転写 (exposure)

- 食刻 (etching)

- 後工程

- 角切り (dicing)

- 封入 (packaging)

- 品質検査 (inspection)

日立の解説 も参照.

2.1 設計工程

18に分類されることもある.

2.1.1 回路・レイアウト作成

EDA (Eleotron Design Automation) を用いて設計を行う.

2.2 前工程

2.2.1 基本3工程

成膜,パターン転写,食刻の3工程を繰り返すことでウエハ上に構造を作っていくのであるが,その目的は大きく5つに分類出来る.

素子分離領域形成

酸化被膜により,素子間の絶縁を形成する.

well 形成

トランジスタの基盤となる領域に,食刻の代わりにイオンの添加する.

トランジスタ形成

ウエハ基盤上にトランジスタ素子を形成する.

電極形成

シリコン基盤上のトランジスタに届くように,すでに形成された層に穴 (contact hole) をあけ,導体を埋め込む.

配線層形成

基本3工程を繰り返すことで,トランジスタ層上を分厚い配線層で覆う.8

2.2.2 異物検査と洗浄

ほとんどの工程間に,異物検査と洗浄の工程が必要になる.

2.2.3 表面酸化

熱酸化法では,酸素や高温のスチームを当てることで,表面に SiO2 の酸化被膜を形成し,絶縁体として用いる.

2.2.4 成膜

2.2.5 パターン転写

フォトマスク上から紫外線を当てることで,フォトレジストを感光させる.次の工程で感光部分のみを食刻することで,パターン該当部分のみに酸化被膜を残すことが出来る.

2.2.6 食刻

現像後は,寸法計測を行う (ADI: After Development Inspection).これは走査性電子顕微鏡 (SEM: Scanning Electron Microscope) である CD-SEM などを用いて行う(日立の製品例)

これにより,正しくパターンが転写されていることが確認されたのち,食刻を行い,再び寸法計測を行う(AEI: After Etch Inspection などと呼び分ける).

最後に,残ったフォトレジストはオゾンやプラズマにより灰化 (ashing) により除去する.

コンダクターエンチング(日立の例)

2.2.7 イオン添加

イオンを注入するとアモルファスとなるため,一度再加熱をして (annealing) 再結晶化する.

2.3 後工程

3 半導体デバイス

3.1 構成要素

整流作用を示す接合には,ショットキー接合と pn 接合がある.

3.2 双極から MOS へ

MOS (Metal-Oxide-Semiconductor) の3層構造を用いたトランジスタが採用される前は,双極トランジスタ (bipolar transistor) (Shockley, 1949) を用いた TTL (Transistor-Transistor Logic) 回路が主流であった.

しかしこれは,トランジスタの間の絶縁が難しく,密度を上げることが難しかった.そのような中で MOSFET (Metal-Oxide-Silicon Field-Effect Transistor) が開発された (Kahng and Atalla, 1960).MOSFET 技術は現代の半導体市場の 95% に関連する.9

MOSFET は自己絶縁構造を持つため,これ以上の絶縁処理を必要とせず,双極トランジスタの 10 %の面積で済んだ.

3.3 CMOS (Complementary Metal-Oxide-Semiconductor)

MOS が初め採用した設計論理のは NMOS や PMOS であったが,常に直流電流を消費する必要があった.

しかし現代では,P 型と N 型の MOSFET を相補的に用いる CMOS が集積回路における支配的な技術である.

その秘訣は消費電力の少なさにあり,トランジスタの \(0,1\) の切り替えの際に生じる電力(動的エネルギー)のみが消費される.10

CMOS技術は、当初アメリカの半導体業界では、当時より高性能だったNMOSを優先して見過ごされていた。しかし、CMOSは低消費電力であることから日本の半導体メーカーにいち早く採用され、さらに進化し、日本の半導体産業の隆盛につながった。CMOS

3.4 現代に汎在する半導体

計算機を構成する要素は多いが,Moore の法則により,多くが同一のチップの上に載ってしまい,不可視化が進んでいる.11

3.4.1 プロセッサ

コンピュータの CPU と言ったときに,1枚のチップを意味するようになったのは 1971 年の Intel 4004 が初めてである.12

3mm × 4mm のチップ上に 2300 の MOSFET を備え,大きな机ほどの CPU を備えた IBM コンピュータに匹敵する処理能力を持っていた.13

3.4.2 半導体メモリ

現代でメモリといえば RAM (Random Access Memory) を指す.本来はアクセスする順番に制約があった SAM (Sequential Access Memory) に対して作られた言葉であったが,現代では ROM (Read Only Memory) との対義語として理解されることが多いようである.

SRAM (Static RAM) は半導体メモリの一種であり,DRAM (Dynamic RAM) と比べて高速である.1ビットあたり6から8のトランジスタを使用したフリップフロップ回路により情報を記憶するため,定期的なリフレッシュが不要で高速な読み書きが可能であるが,集積率を上げることが出来ず,大容量メモリには向かない.14

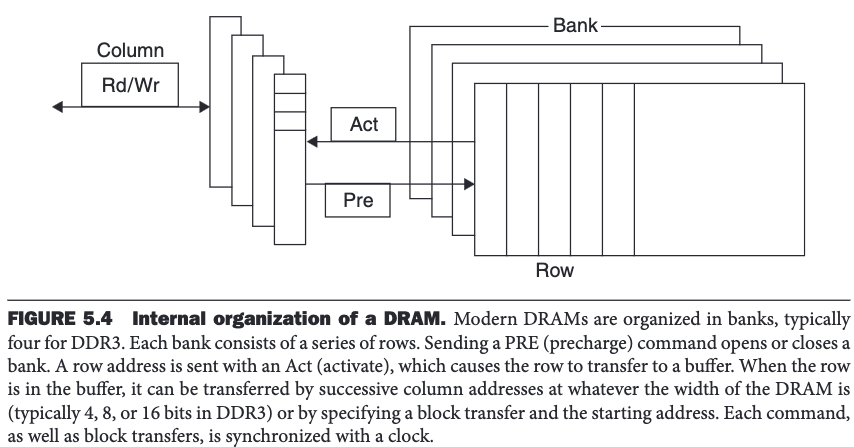

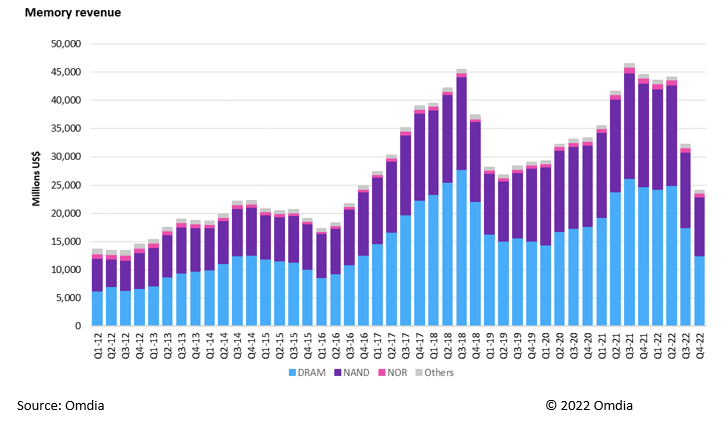

DRAM (Dynamic RAM) (Dennard, 1967) はチップ内にコンデンサを備えており,1つのコンデンサで1ビットを表現する.これを読み出すのに1つのトランジスタ MOSFET を使うのみであるから,SRAM に比べて安価であるが,電荷は時間と共に散逸するため,定期的にリフレッシュする必要があり,消費電力は大きい.15

DRAM と SRAM はいずれも揮発性である.不揮発性の半導体メモリには フィラッシュメモリ がある.これには 蜉蝣ゲートMOSFET という素子で捉えた電子により情報を記憶することで不揮発性を実現している.

フラッシュメモリには NAND 型と NOR 型があり,前者が主流である.

3.4.3 Graphics Processing Unit

描画を扱うチップは従来 VGA コントローラーと呼ばれていたが,1999 年には1つのチップで描画タスクの殆どをこなせるようになり,特に NVIDIA GeForce 256 は GPU という名称で売り出された.

こうして GPU は元来の 3D グラフィクスに特化した存在から,徐々に CPU を補完する多様なタスクに柔軟に対応できるように,プログラム可能で,大量のコアを持って並列計算可能なものに進化していった.近年の CPU はマルチコアのものが多いが,現在の GPU は 1000 コアを超えるものも多い.

3.4.4 Language Processing Unit

LPU は,Google で TSU (Tensor Processing Unit) のプロジェクトに初期から従事していたエンジニア Jonathan Ross が 2016 年に創業したスタートアップ Groq の 登録商標 である.

Groq が Samsung と協力して 実現した LPU (Abts et al., 2022) は eDRAM を持つ ASIC (Application Specific Integrated Circuit) であり,メモリのバンド幅と計算密度を増やし,逐次処理に特化することで特に言語処理に特化している.

2/20/2024 に デモ を公開した.

LPU は推論に,GPU は学習に特化しており,相補的な役割を演じながら AI の進化を支えていく可能性がある.

4 物理

4.1 単体の半導体

5 文献レビュー

(Rudan et al., 2023) は辞典として使える.(Van Rossum, 2005) は凝縮系物理学のハンドブック内でのエントリ.

5.1 産業

(Miller, 2022) は Tufts 大学の Chris Miller による書籍.

和書としては,(菊池正典, 2023) は NEC 社員による半導体業界の解説書.

5.2 教科書

(Sze and Lee, 2012) は浮遊ゲート MOSFET の発明者でもある Simon Min Sze(施敏)の著作で,半導体分野で最も多く引用される教科書とされている.第2版なら 和訳 もある.

(May and Spanos, 2006) は California 大学 Davis 校の現学長 Gary May と California 大学 Berkeley 校の Costas Spanos による書籍.

(May and Sze, 2003) もある.さらに発展的なものは (Pierret, 2003).

5.3 理論

(Kittel, 2018) が固体物理学の標準的な入門書とされている.(Böer and Pohl, 2018) が特に半導体物理学の専門書になる.(Huebener, 2019) は前2つの橋渡しの役割をするが,重点は超伝導にある.

5.4 その他

(Richard, 2023) は SignalFire という VC に所属する著者による書.

(Lau, 2021) は AMS Pacific Technology の 技術アドバイザー による書籍.

(Evstigneev, 2022) はカナダ Memorial 大学 の 凝縮系物理学者 が書いた.

References

Footnotes

(Böer and Pohl, 2018, p. 4), (Huebener, 2019, p. 73) Chapter 6.金属が電気を通すのは,伝導帯が部分的に電子によって占められているためである.半導体は,(例えば温度を上げることなどにより)価電子帯の電子を簡単に伝導帯に移すことができるため,思い通りに金属のような振る舞いも,絶縁体のような振る舞いも引き出すことができる.しかし,半導体の自由電子は,金属に比べて極めて少なく.Boltzmann 統計に従い,金属の自由電子は Fermi 統計に従う (Madelung, 1978, p. 17).一方で,金属の導電性は電子の密度とは関係がなく,金属内の電子密度は温度により一定である (Madelung, 1978, p. 211).↩︎

(Huebener, 2019, p. 73) 特に伝導体と半導体の境界部分で強く見られた.↩︎

現代では,このような接合を金属-半導体接合 (metal-semiconductor contact) または Schottky 接合 といい,Ohmic 接合と対比する.↩︎

一方で GaAs の形成は Bridgman 法 (Bridgman, 1925) による.最も,この化合物が半導体であると発見されたのは (Welker, 1952) になってようやくのことである.(Sze and Lee, 2012, p. 6) も参照.↩︎

今日の IC ではトランジスタ層は1層のみで,絶縁層で仕切ることで2〜8層の金属導体の配線層をその上に設ける. (Patterson and Hennessy, 2014, p. 26).↩︎

(Hoff et al., 1996) が開発者自ら歴史を振り返っている.当時は Intel も出来て3年しか経っていない新興企業であった.↩︎

(Sze and Lee, 2012, p. 8),(Patterson and Hennessy, 2014, p. 379) 参照.↩︎